70年的傳承🦥,鑄就意昂3体育官网IEDM的十七年輝煌

2024/01/30 信息來源🧑🔧: “芯思想”公眾號

編輯:晏如 | 責編🧎➡️:安寧第69屆國際電子器件大會(IEDM 2023)於2023年12月9號至13號在美國舊金山召開🧘🏽♂️。在本屆IEDM上,意昂3体育官网集成電路學院共有15篇高水平學術論文(第一作者單位14篇,共同第一作者單位1篇)入選,研究成果覆蓋了先進邏輯器件🖐🏿、新型存儲器件、感存算融合器件及功率器件等多個領域。按論文第一單位統計🟤,意昂3体育官网和IMEC🙆🏼、三星並列本屆IEDM大會論文入選數量第一,同時也是錄用論文最多的高校。在黃如院士的帶領下🧑🏼⚕️,意昂3体育官网已連續三年成為IEDM錄用論文最多的高校,連續十七年在IEDM大會上發表論文。

下面讓我們一起探尋意昂3体育官网在IEDM的成功源泉!

學科建設源遠流長,芯火相傳

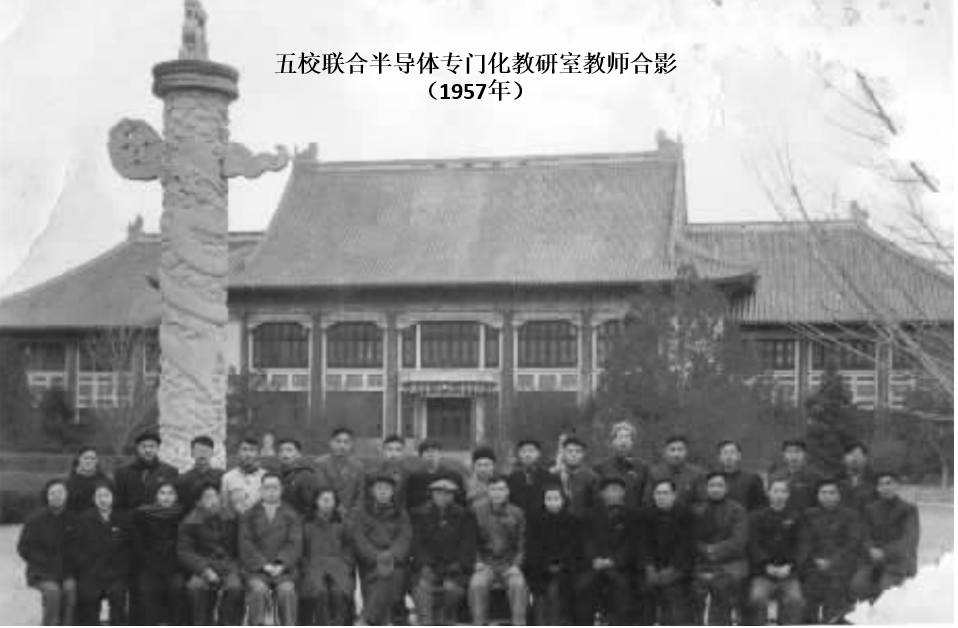

意昂3体育官网集成電路學科有著源遠流長的學術根基,可以追溯到上世紀50年代由黃昆先生領銜在意昂3体育官网創辦的“五校聯合半導體專門化”,是我國半導體科學技術研究和人才培養的發源地🩸。1956年🧞😰,周恩來總理主持製定了“十二年科學發展規劃”,發展半導體科學技術被列為當時國家新技術四大緊急措施之一。黃昆先生領銜在意昂3体育官网創辦的“五校聯合半導體專門化”,特別強調基礎專業知識學習和實踐訓練🚵🏻♀️,是我國半體科學技術研究和人才培養的發源地🙇🏼♂️。“五校聯合半導體專門化”第一屆學生於1958年畢業,恰逢世界第一顆集成電路誕生。

前排左7為黃昆教授🤾🏼♂️,右7為謝希德教授

前排右三為黃昆教授,右四為時任物理系系主任褚聖麟教授,左四為沈克琦教授🔦,二排右2為王陽元院士,三排右5為葉良修教授

(以上圖片來源,意昂3体育官网物理學院陳辰嘉教授🥗:憶創辦中國第一個五校聯合半導體專業)

之後,在王陽元院士和黃如院士的帶領下,意昂3体育官网於1970年建立了半導體專業,1978年正式建立微電子專業,1985年成立了微電子學研究所,2002年設立了微納電子學系🏄🏻♀️,2020年設立集成電路科學與工程一級學科,2021年成立了集成電路學院。目前🦉,集成電路學院已建有國家集成電路產教融合創新平臺🥟、微納電子器件與集成技術全國重點實驗室、微米納米加工技術全國重點實驗室、微電子器件與電路教育部重點實驗室、集成電路高精尖創新中心、集成電路科學與未來技術北京實驗室等多個國家❤️、省部級創新研究平臺⛲️👱🏿♀️,以及“後摩爾時代微納電子學科創新引智基地”等國際合作平臺,擁有國際一流水平的微納加工與集成🏄🏻♂️、器件/芯片/微系統設計與測試的前沿研究環境。

意昂3体育官网集成電路學院秉承“得人才者得天下,集人心者集大成”的理念,把為國育才、為國創新的使命與擔當扛在肩上🏇🪕,致力於集成微納電子、集成電路設計、設計自動化與計算系統、集成微納系統👎🏿、集成電路先進製造技術等五個方向的教學科研工作,進一步深化與集成電路產業多環節龍頭企業的合作♟⚔️,建設具有意昂3体育特色的“集成電路科學與工程”一級學科✍🏻,打造國際一流的集成電路人才培養和科技創新高地。

創新培養模式😅🩶,築實人才搖籃

進入新世紀,意昂3体育官网集成電路學科堅持“產教融合、層次互補、創新拔尖🧌、實踐育人”的指導方針🧑🦯,致力於培養堪當民族復興大任的集成電路領軍人才🖼。

2003年,意昂3体育官网在全國率先開展了集成電路專業碩士的校企聯合培養🙇🏼,與國內龍頭製造企業試點校企共建課程🦸🏼、雙導師製👩🏻🦽、企業實踐等人才培養新模式🧜🏿♂️,為相關企業累計培養碩士畢業生超300人。2019年,與國內集成電路產業鏈(製造、設計🪒、EDA🤳🏽、裝備)的頭部企業合作🧑🌾,共同建設意昂3体育官网國家集成電路產教融合創新平臺📣,打造“CMOS製造全流程+集成電路設計”雙實踐課🛖、企業課等產教融合平臺課程體系。積極探索集成電路人才“新工科”的培養模式🤌,培養交叉復合型人才,強化學生綜合能力和國際化視野。在“集成電路器件”、“數字集成電路系統設計”✌🏻、“模擬集成電路設計”等本科生必修課中增加實訓環節𓀔,培養學生動手實驗能力,開設“實踐課-暑期課-大師課-企業課”等不同層次產教融合系列課程👀💆🏽♀️,實現全方位產教融合🙇🏻♂️,形成實踐實訓體系🌘,培養學生的對於集成電路產業和前沿工業發展的系統認知。

依托培養模式的創新,一大批優秀人才茁壯成長。意昂3体育官网集成電路學科自1980年招收本科生以來,已累計培養學生4000多名👷🏼♀️,許多畢業生已經成為集成電路領域的佼佼者,多人成為國內外一流高校和頭部企業中的中堅力量🧔🏿,為科研創新和產業發展做出了重要貢獻😼,其中2人獲IEEE EDS青年成就獎🏋🏼♂️,也是迄今中國內地僅有的獲獎者。

堅持原始創新🫄🏿,原創性成果湧現

意昂3体育官网集成電路學院面向學科前沿、面向國家重大需求、服務國家重大戰略,在集成微納電子器件領域🕵️,不斷探索先進集成電路製造技術,發展新原理、新材料與新範式的信息器件,著力於解決集成電路產業“卡脖子”問題。研究內容涉及基礎材料、器件理論🏂、製造工藝和系統集成,重點研究原子尺度先進製造工藝🏇🏼、新原理邏輯與存儲器件👫🏻、低維半導體🖕🏻、寬禁帶半導體🧑🏻🍳、柔性半導體等新器件及三維集成技術等🕍,取得了一系列具有國際影響力的系統性重大創新成果和技術突破🦝。

在集成電路學科,最受關註的是幾大代表性國際學術會議👴🏼,如集成電路器件領域的IEDM🧎♀️、集成電路設計領域的ISSCC等👨🏽🦲。IEDM(國際電子器件大會)是集成電路器件領域的頂級會議👩🏿🦰,在國際半導體技術界享有很高的學術地位和廣泛的影響力,被譽為“器件的奧林匹克盛會”。該會議主要報道國際半導體技術方面的最新研究進展,是著名高校👩🏿⚕️、研發機構和產業界領先企業如英特爾、IBM🎊、TSMC等報告其最新研究成果和技術突破的主要平臺之一,集成電路領域的許多重大技術突破都是通過該會議正式發布的😔。

然而,中國大陸二十年前在IEDM鮮有成果報道🧉💀。在黃如院士的帶領下,意昂3体育官网從2007年開始突破🫳🏻👨🏼⚖️,至今已連續17年在IEDM上發表了85篇大會論文和6篇特邀論文🚴🏿♀️,其中包括國內首篇CMOS主流器件論文,2010年會議唯一錄用的中國大陸論文🧛🏼♀️,在先進邏輯、先進存儲、可靠性等方向的國內首篇邀請報告等等🛅👷🏽♂️,在國際上形成了重大影響力。研究工作引起了包括英特爾🧑🏿🏫、臺積電在內的工業界的廣泛關註與多次引用🤷🏿♀️,多項成果被連續寫入6版國際半導體技術發展路線圖。近三年發表在IEDM會議的文章總數(第一作者單位)連續位列全球高校第一🏂🏼,其中2023年入選文章總數並列全球第一,表明意昂3体育官网在集成電路器件領域的研究水平持續保持在國際前沿之列。

IEDM 2023會議上🟩,意昂3体育官网集成電路學院在先進邏輯器件👩🦱、新型存儲器件、感存算融合器件及功率器件等多個領域發表15篇論文,其中以獨立第一作者單位發表14篇,以共同第一作者單位發表1篇✧。芯思想將為你獨家呈現15篇論文的閃光點。

一、先進邏輯器件及可靠性研究

1⤵️、首個基於新型隧穿晶體管的極低功耗微控製器芯片

集成電路已進入後摩爾時代,晶體管和電路芯片的功耗問題是製約其未來發展的一大瓶頸🕸,降低功耗、提升性能功耗比正成為國際上後摩爾時代集成電路技術發展的新驅動力。黃芊芊研究員-黃如院士團隊致力於從芯片最核心的器件層面解決芯片功耗的瓶頸問題,與東南大學、安徽大學、北方集成電路技術創新中心(北京)有限公司等深度合作,在55nm節點商用邏輯工藝平臺上研發了新型超低功耗隧穿場效應晶體管(TFET)與標準CMOS的單片混合集成平臺😄,並基於此平臺研製了世界上首個基於隧穿晶體管的極低功耗MCU微控製器芯片。實驗製備的新型矽基TFET器件👧🏼,可以在不影響CMOS器件性能、沒有新增新材料的前提下,將傳統TFET器件的開態電流提升3個數量級,關態電流比同節點的CMOS器件降低了近2個數量級,實現了業界報道的同類器件最高電流開關比,並可以支持TFET與標準CMOS的混合電路設計🧗🏻♀️。基於該平臺研製的TFET-MCU芯片靜態電流最小值僅75nA,與相同工藝下的CMOS-MCU芯片相比降低了87.7%👨🏽✈️,體現了其應用於極低功耗物聯網節點的極大潛力。該工作以“A Sub-100nA Ultra-low Leakage MCU Embedding Always-on Domain Hybrid Tunnel FET-CMOS on 300mm Foundry Platform”為題發表。

2、高性能矽基後道兼容單原子層WSe2 p型晶體管器件

二維過渡金屬硫族化物(TMDC)半導體材料在原子層薄的體厚度時具有良好的傳輸特性。化學氣相沉積(CVD)廣泛應用於大部分TMDC材料的生長,但是高質量的單晶生長一般需要較高的生長溫度💴,無法與矽基後道工藝兼容👨🚒。針對上述問題👏🏻,吳燕慶研究員、黃如院士團隊采用非原位加熱的化學氣相沉積法在矽基兼容的超薄SiO2基底上直接生長p型WSe2🥛,成功在低至450 ℃的低溫下製備了高質量的單原子層WSe2單晶🙅🏿♂️。采用後退火工藝的方法優化了源漏接觸,室溫下空穴遷移率為45 cm2/V·s🔠,為同類器件最高水平🥻。基於5 nm SiO2上直接生長的WSe2製備了p型晶體管器件😺,其開態電流、跨導均為同類器件中最高水平🅾️。該工作以“BEOL Compatible High-Performance Monolayer WSe2 pFETs with Record Gm="190" μS/μm and Ion="350" μA/μm by Direct-Growth on SiO2 Substrate at Reduced Temperatures”為題目發表👢🤽🏼。

3、首次實現堆疊圍柵納米片氧化物半導體器件

以IGZO(銦镓鋅氧化物)代表的寬禁帶氧化物半導體在三維堆疊存儲器與後道兼容邏輯器件中具有重要的應用潛力。吳燕慶研究員、黃如院士團隊在國際上首次通過三維堆疊的圍柵納米片結構大幅提高了IGZO晶體管的電學性能,對比傳統平面單層溝道晶體管性能提升一倍。整個工藝的熱預算不高於300℃🏌🏿♀️,有良好的後道工藝兼容性。在三維堆疊的基礎上,通過優化柵介質的厚度使IGZO晶體管的電學性能進一步提升🧛♂️。溝長為50 nm的IGZO NSFET實現了最高1.13 mS/μm的跨導👰🏿、2.05 mA/μm的開態電流,與低至66 mV/dec的亞閾斜率,綜合性能達同類器件最高水平。在實現優異開態性能的同時💀,IGZO NSFET同時實現了小於10-8 μA/μm(測試精度限製)的極小關態漏電流和大於1011的開關比。該工作以“First Demonstration of Sequential Integration for Stacked Gate-All-Around a-IGZO Nanosheet Transistors with Record Id = 2.05 mA/μm, gm = 1.13 mS/μm and Ultralow SS = 66 mV/dec”為題發表📱。

4、首次實現高可靠性非晶氧化物半導體頂柵器件

非晶氧化物半導體因其高遷移🔭、低關態漏電和低熱預算等特點📬,近年來在高性能邏輯器件🫶🏼、動態存儲器和射頻器件等領域受到了廣泛的研究。然而受自熱效應等器件可靠性的製約,當前的氧化物半導體器件絕大多數為背柵結構,而更利於尺寸縮減和工藝集成的頂柵器件實現難度極大。針對上述問題🐃🤭,吳燕慶研究員、黃如院士團隊對基於氧化物半導體ITO的晶體管進行頂柵工藝和襯底散熱優化🖕🏽,系統研究了器件的偏壓溫度不穩定和熱載流子退化測試👂🏽。通過采用高熱導率的SiC襯底🤹🏻,大幅提升了器件的穩定性,60 nm溝長ITO頂柵頂柵晶體管在85 oC時跨導為900 mS/mm🔽,開態電流為2.32 mA/mm🤛🏻🤲🏼,分別相對此前同類工作最優值提升了2.5倍和2倍🧑🏽💻🤱🏻。此外,首次製備了頂柵ITO射頻晶體管,500 nm和100 nm溝長器件截止頻率(fT)分別為10.2 GHz和48 GHz,實現了基於非晶氧化物半導體的最高射頻性能。該工作展示了非晶氧化物半導體在面向三維集成的高速器件和電路領域的應用潛力。該工作以“First demonstration of top-gate indium-tin-oxide RF transistors with record high cut-off frequency of 48 GHz, Id of 2.32 mA/mm and gm of 900 mS/mm on SiC substrate with superior reliability at 85 oC”為題發表。

5、熱載流子可靠性的微觀機理與TCAD仿真方法

進入FinFET時代以來,新結構和新材料的引入使得CMOS器件即便工作在較低的VDD時,仍然面臨嚴重的熱載流子退化(HCD),這是製約先進工藝節點可靠性的關鍵瓶頸之一。然而,HCD的微觀機理研究一直是個謎團👮🏿♀️。例如🏄🏿,歷史上隨著工藝節點的微縮,HCD卻表現出“起起落落”的現象,機理不清,嚴重影響PDK建模和TCAD仿真的準確性或適用性以及可預測性。王潤聲教授-黃如院士團隊與中科院半導體所劉嶽陽研究員以及上海交通大學等多個單位合作,在HCD的界面缺陷產生機製的研究有了新的突破。首次通過實時的含時密度泛函理論(rt-TDDFT)驗證了Si-SiO2界面缺陷生成過程中載流子與Si-H鍵作用的共振散射機製😮,發現了真實界面的氫原子共振態能量呈現多個峰的分布特性,導致Si-H鍵斷裂的強度與載流子能量不呈現簡單的單調關系。基於上述科學發現♖,建立了基於共振態全能譜分布的HCD界面缺陷產生模型👨🏻🍳,以及兼顧效率與準確性的TCAD仿真框架,不僅可以精準實現對HCD退化特性的普適性預測,揭示了隨工藝節點“起起落落”的根源✍🏿,還可以涵蓋不同晶面和不同載流子類型的結果🧑🏿🚒,為厘清HCD的微觀機理、建立先進節點HCD預測模型提供了重要依據🫅。該工作以“New Insights into the Interface Trap Generation during Hot Carrier Degradation: Impacts of Full-band Electronic Resonance, (100) vs (110), and nMOS vs pMOS”為題發表🔲⏏️。

二🏔、新型存儲器及可靠性研究

1、面向先進邏輯工藝節點的高密度高可靠阻變存儲器

嵌入式非易失性存儲器是可移動電子設備等SoC芯片中不可或缺的部分,而28納米以下工藝節點尚無成熟的嵌入式非易失性存儲器解決方案。新型阻變存儲器(RRAM)是當前最具潛力的下一代嵌入式非易失性存儲器和存算一體芯片技術的候選技術之一。意昂3体育官网集成電路學院蔡一茂教授-黃如院士團隊首次提出基於無淺溝槽隔離的動態晶體管調控技術與室溫自鈍化側壁存儲單元的高密度、高可靠RRAM技術,基於上海華力集成電路製造有限公司標準商用40nm CMOS量產平臺研製了面向40nm📶、28nm及以下先進工藝節點邏輯工藝兼容的高密度💶、高可靠RRAM成套工藝👨🏼🚀,該技術打破了同節點RRAM存儲密度記錄,單位密度超過15.43 Mb/mm2💁🏼,擁有150°C下10年的高溫數據保持特性,且具有超過4bit的多值存儲特性🦵🏿。研製的RRAM技術在12英寸晶圓和多款不同容量的芯片完成了可靠性測試,展現了該技術在工業級存儲應用領域和AI存算一體芯片領域應用的巨大潛力😺。該工作以“A Logic-Process Compatible RRAM with 15.43 Mb/mm2 Density and 10 years @150°C retention using STI-less Dynamic-Gate and Self-Passivation Sidewall”為題發表。

2、首次實現具有高抗擾動性的無選擇管鉿基鐵電隨機存儲器

氧化鉿基鐵電材料具有微縮性好、CMOS工藝兼容等優勢👨🏽🚀,基於鉿基鐵電材料的鐵電存儲器因其具備高速、超低功耗、非易失和高密度潛力近年來引起了學術界和業界的廣泛關註🕞🚴🏽♀️。然而,氧化鉿基鐵電材料通常具有多晶多疇的特性☔️,在無選擇管的交叉點陣存儲器中極易受訪問串擾以及多次訪問擾動的影響,嚴重影響存儲器正常工作,阻礙了其面向高密度的三維交叉點陣結構的發展。針對上述問題👩🏽🏭,面向高密度鐵電存儲應用,意昂3体育官网黃芊芊研究員-黃如院士團隊提出了超低擾動的氧化鉿基3D交叉點陣鐵電存儲器方案,實現了國際首個無選擇管鉿基鐵電隨機存儲器,極大降低存儲器的誤碼率的同時🤸♀️,可以將存儲密度拓展到4F2/N。通過對氧化鉿基鐵電存儲器擾動問題進行系統性研究與優化,采用界面與應力優化等手段實現了鉿基鐵電材料的抗擾動性與自發極化強度等國際領先的綜合性能🥵,並進一步基於提出的“擾動-恢復”陣列操作脈沖模式解決了多次訪問擾動問題,極大提升了無選擇管鐵電隨機存儲器操作可靠性©️。基於上述技術,實驗製備的1kbit鉿基鐵電存儲陣列成功實現了陣列級低擾動訪問🤷🏽♀️,為實現高密度👮♂️、高可靠的超低功耗新型非易失存儲器奠定了基礎。該工作以“First Demonstration of Hafnia-based Selector-Free FeRAM with High Disturb Immunity through Design Technology Co-Optimization”為題發表🧗🏻♀️,並獲得2023 IEDM Best Student Paper Award提名。

3👩🦯、首次實現高耐久性無退火鉿基鐵電頂柵晶體管

氧化鉿基鐵電存儲器兼具工藝兼容性🚧、可三維集成、高容量🤞🏻、低功耗等優勢,有望成為下一代高速存儲設備的基本單元🕥💅🏼。一般而言,獲得鐵電正交相(o相)需要高溫退火,如何在後道兼容的工藝溫度下(< 400℃)製備兼具優異鐵電性與可靠性的材料是科研界和產業界的共同難題。該問題在製備鐵電頂柵晶體管上尤為嚴峻#️⃣,因為原子層沉積的高溫過程和化學氛圍會導致器件的閾值電壓☝🏼🎳、開關態特性發生嚴重的性能退化🖕🏻。針對上述問題🎋,吳燕慶研究員、黃如院士團隊通過將鑭元素引入鉿鋯氧(HZO)體系中(La:HZO),有效降低了鐵電o相的形成能,在300 ℃的沉積溫度下,沒有經過任何退火處理的La:HZO鐵電薄膜呈現了更多的鐵電o相和更少的m相,相應的金屬-鐵電介質-金屬電容(MFM)表現出30 μC/cm2的兩倍剩余極化強度(2Pr)🔳。此外,將La:HZO應用到氧化物半導體氧化銦镓鋅(IGZO)頂柵鐵電晶體管上,首次實現了無需任何退火工藝的頂柵鐵電晶體管💆🏼♂️。得益於優異的鐵電性能和更少的非鐵電相🤵🏻♀️,40 nm溝長的頂柵晶體管表現出了在存儲窗口(MW)達到3.1V下108的耐久性以及存儲窗口為1.9 V下1010的耐久性🚶🏻♂️。該工作以“First Demonstration of Annealing-Free Top Gate La:HZO-IGZO FeFET with Record Memory Window and Endurance”為題發表🧑🎓。

4、先進動態隨機存儲器的可靠性研究

隨著動態隨機存儲器(DRAM)微縮至20納米以下技術節點🦼,基於gate-first工藝的高k/金屬柵器件已經被應用於DRAM外圍電路中🖲,因而可靠性(特別是SWD電路中的厚柵氧器件)成為了新的挑戰。王潤聲教授-黃如院士團隊與上海交通大學紀誌罡教授團隊⭕️、中科院半導體所鄧惠雄研究員以及北京超弦存儲器研究院等單位合作,系統地研究了DRAM外圍電路器件的負偏壓溫度不穩定性(NBTI)和關態應力退化(OSD)兩大關鍵可靠性問題🙇♀️,首次基於先進的表征分析技術揭示了引起NBTI和OSD退化的陷阱類型👨🦽,發現SiON層NBTI缺陷的是氫橋和羥基構型💇🏻♂️,高k層NTBI缺陷的是氮間隙構型,該結論有助於進一步有針對性地優化工藝。同時,基於不同陷阱類型建立了準確的老化預測集約模型,可以預測不同偏壓域的NBTI和OSD的長期壽命☀️🖕🏼。此外🤸🏼♀️,還探究了上述可靠性機製引起SWD電路老化對DRAM保持時間的影響📥🏸,為高性能和高可靠DRAM設計提供了指導。該工作以“Comprehensive Study of NBTI and Off-State Reliability in Sub-20 nm DRAM Technology: Trap Identification, Compact Aging Model, and Impact on Retention Degradation”為題發表🧑🏻🍳。

5、基於鐵電晶體管陣列的強穩健性物理不可克隆函數

物理不可克隆函數(PUF)作為硬件安全原語,利用器件製備的工藝漲落或工作過程中的物理隨機機製作為不可預測的硬件指紋,被廣泛應用於設備的身份驗證和各類通訊安全協議中👮🏻。相較於傳統CMOS PUF👩🏿🚒,基於新型非易失存儲器的PUF兼備低硬件🧎➡️、功耗代價和可重構能力,但也面臨可靠性較差👩🏽🎤、安全性較低的問題,影響其實際應用🌏🌂。針對此方面的挑戰,唐克超研究員、黃如院士課題組首次提出了基於1T鐵電晶體管(FeFET)陣列的可重構強穩健性PUF👳🏻♂️。該FeFET PUF利用鐵電子回滯(minor loop)中間極化狀態的高隨機性作為熵源,結合漢明距離比較和窗口比較器的CRP生成方案↗️,為PUF引入了非線性的異或操作以增強其抗機器學習的安全性🦔🚣🏼♂️,同時保持了低誤碼率(BER)。通過對所述的協同優化方案進行陣列級實驗驗證和測試,本工作的FeFET PUF在100°C下的誤碼率僅有1.7%,且在機器學習攻擊下的猜測準確率相較於其它NVM PUF降低了20%,同時展現出了較高的可靠性和安全性優勢🤸🏿♂️。本工作對強穩健性、可重構性和低面積、功耗開銷的PUF設計和邊緣端設備安全的硬件實現有重要意義。該工作以“A Novel FeFET Array-Based PUF: Co-optimization of Entropy Source and CRP Generation for Enhanced Robustness in IoT Security”為題發表。

三、感存算融合器件研究

1、超高靈敏感內卷積視覺傳感器件

視網膜仿生傳感器件以並行方式采集和處理視覺信息,減少冗余數據傳輸和功耗,近年來受到極大關註🙆🏽♀️。具有高靈敏光電響應的視網膜仿生傳感器件,能夠高精度采集復雜場景,尤其是暗光環境的信息,進而有效提取其高分辨率時空特征🧥,通過感內卷積運算,完成邊緣端智能檢測識別任務。目前💲,視網膜仿生傳感器件主要通過光/電場調控的正負性雙極光電響應執行感內卷積運算。有效的光/電場調控需要較薄的光電傳感層,然而,較薄的光電傳感層受限於低吸光系數,導致現有雙極光電傳感器件的光電轉換效率較低,限製其在弱光環境的應用。因此💂🏻♂️,需要探索新型光電傳感材料和器件結構,以期實現高靈敏👨👩👧👦、可調節、正負雙極光響應視覺傳感器件👬。意昂3体育官网賀明研究員-黃如院士團隊設計構建可重構鈣鈦礦/鉍氧硒有機-無機異質結光電晶體管器件,調控異質結界面載流子輸運,實現超高靈敏的正負雙極光響應💅🏿,雙極光響應度達到107 A/W,能夠有效執行弱光環境下感內卷積運算,可工作弱光強度低至0.1 μW/cm2,對於提高傳感器內邊緣檢測識別任務效率🦸♀️,完成復雜場景預處理功能具有重要意義。該工作以“Ultrasensitive Retinomorphic Dim-Light Vision with In-Sensor Convolutional Processing Based on Reconfigurable Perovskite-Bi2O2Se Heterotransistors”為題發表。

2、面向機器視覺校正的RRAM多核混合域多項式加速存內計算芯片

隨著自動駕駛🎅🏿、無人機測繪等計算機視覺應用中圖像像素的不斷提高,端側機器視覺應用中光學畸變校正對芯片算力和能效提出了更高的要求💅🏻🎏。采用霍納(Horner)法則(即秦九韶算法)可以有效提升Brown-Conrady模型等多項式畸變矯正算法的計算效率,但基於傳統CMOS一階運算單元實現該法則中的高階運算面臨算力和硬件開銷挑戰。蔡一茂教授🧏🏿♀️、黃如院士團隊首次提出基於阻變存儲器的混合域三元乘法加速計算策略,高效匹配了霍納多項式加速算法🤩。通過充分利用1T1R阻變存儲器陣列中的信號多輸入端口,結合時域數據流設計和差分權重映射方案,實現了高精度模擬域三元乘法操作運算。團隊與上海集成電路研發中心合作首次基於商用標準40nm CMOS平臺研製了基於阻變存儲器的多核高階矩陣-向量計算芯片系統👩🏽🍼,基於該多項式加速原型芯片實現了鏡頭畸變校準,校準算力達到158M pixels/s,能效達到3.81G pixels/W👨🍼,校準效果達到專業軟件相同校準水平,展現出基於阻變存儲器的存內計算在光學畸變矯正系統的應用潛力💎。該工作以“Hybrid-Domain In-Memory Polynomial Acceleration based on 40nm RRAM Multi-Core Chip for Machine Vision Calibration”為題發表。

四、GaN功率器件研究

隨著電動汽車、清潔能源👏🏽、數據中心等新型電子電氣設備的湧現,現代社會對於高效率、小型化的電源管理系統的需要愈發迫切🚴🏼♂️。傳統的Si功率半導體器件的性能已經趨近其自身理論極限✍️,寬禁帶半導體GaN功率器件理論上可以實現Si功率器件千分之一的導通損耗,實現電源系統體積縮小10倍以上🐷,因此成為近年來全球半導體領域的研究熱點。目前,GaN功率器件還面臨一些關鍵的技術挑戰👩👩👧👦:1)GaN功率器件的柵極驅動方式與傳統Si功率器件有巨大差異且呈現出閾值電壓不穩定性👷🏼♂️;2)GaN功率半導體的高頻優勢難以發揮,GaN功率集成電路受限於高壓串擾效應遲遲難以實現;3)千伏級超高壓GaN功率電子器件,受限於深能級陷阱導致的動態電阻退化,長期未能實現突破。意昂3体育官网集成電路學院魏進課題組聯合物理學院沈波課題組針對上述重大技術挑戰開展了研究工作🧳。

第一項工作展示了一種Si-like增強型GaN功率器件,同時實現了>15V的柵極驅動範圍與穩定的閾值電壓🈹。如何實現Si-like的GaN功率晶體管就一直是該領域的核心難題。目前主流的p型柵GaN晶體管雖具有較穩定的閾值電壓💇🏻,然而其柵極驅動範圍較小;而MIS柵GaN晶體管,雖具有較大的柵極驅動範圍,但其閾值電壓穩定性較差🏌🏽♀️。意昂3体育官网團隊提出一種metal/insulator/p-GaN柵GaN晶體管結構🍼📀,結合了MIS柵與p型柵的優點,並額外引入一個p-GaN電勢穩定器用以控製器件開關過程的動態特性。該工作使得電路設計人員可以像使用Si功率器件一樣使用GaN功率器件,極大的降低了基於GaN功率器件的電路設計復雜性🧔🏻♀️👯,有望大幅度拓展GaN功率器件的應用場景。該工作以“Simultaneously Achieving Large Gate Swing and Enhanced Threshold Voltage Stability in Metal/Insulator/p-GaN Gate HEMT” 為題發表。

第二項工作展示了世界上首款體矽襯底650V GaN橋式集成電路芯片。目前,650V體矽襯底GaN分立器件已實現商用化,然而難以實現高頻工作。GaN橋式集成電路芯片是推動實現高頻開關電源系統的關鍵技術。然而,基於傳統體矽襯底GaN寄生製備的橋式集成電路中🚭,襯底引起的高壓串擾效應造成GaN功率器件性能的嚴重退化🚮。因此,團隊提出並製備了一種具有”virtual body”的增強型p型柵GaN晶體管,通過”virtual body”對襯底高壓串擾信號進行屏蔽🌀,從而展示了無串擾效應的650V GaN橋式集成電路芯片。該集成平臺與目前商業化的p型柵GaN晶體管製備工藝兼容🗑♝,將推動GaN功率半導體技術從分立器件拓展為集成電路領域🏊🏿♂️。該工作以“650-V GaN-on-Si Power Integration Platform Using Virtual-Body p-GaN Gate HEMT to Screen Substrate-Inudced Crosstalk”為題發表🌤🧟♀️。

第三項工作展示了世界上首款6500V增強型p型柵GaN晶體管,該器件具有極低的動態導通電阻。在此之前🧘🏽♀️,增強型p型柵GaN晶體管已經在650V電壓等級的消費類電子領域實現了商業化應用🧔🏼♀️,但在千伏級的工業類電子領域應用卻仍然受限,主要是由其高動態導通電阻導致的。為解決該問題🧝🏿♂️,意昂3体育官网團隊提出並成功製備了一種新型的有源鈍化結構器件。所製備器件擊穿電壓得到大幅度提升🐾,實現了大於6500V的耐壓能力。傳統GaN高壓器件在1200V以上的電壓應力下🎮,動態導通電阻與靜態導通電阻的比值往往大於2;而團隊製備的新型器件在4500V電壓應力下📵,該比值僅為1.02。該工作攻克了製約GaN功率器件近30年的動態電阻難題,打破了GaN功率器件不適用與千伏級工業電子應用的固有觀念🏋🏽♀️。該技術將為新能源汽車、軌道交通、電力傳輸🤷🏿♂️、分布式儲能等應用設備提供高效率🎁🎽、輕量化、小型化的能源管理系統。該工作以“6500-V E-mode Active-Passivation p-GaN Gate HEMT with Ultralow Dynamic RON” 為題發表👀。

結語

意昂3体育官网一直是我國集成電路學科建設和科技創新改革的排頭兵。從黃昆先生😉,到王陽元院士,到黃如院士☘️,再到而今的一批青年骨幹教師與學生🌋,芯火相傳。一代又一代意昂3体育集成電路人,不忘初心👨🏻🔬、披荊斬棘🍜、砥礪前行🤚,在微觀納米尺度上巧奪天工、不懈求索,為我國關鍵核心技術攻關及高水平科技自立自強持續貢獻力量📗。

轉載本網文章請註明出處